- 您现在的位置:买卖IC网 > Sheet目录2000 > IDT5V49EE904NLGI8 (IDT, Integrated Device Technology Inc)IC PLL CLK GEN 200MHZ 32VFQFN

IDT5V49EE904

EEPROM PROGRAMMABLE CLOCK GENERATOR

CLOCK SYNTHESIZER

IDT EEPROM PROGRAMMABLE CLOCK GENERATOR

23

IDT5V49EE904

REV P 092412

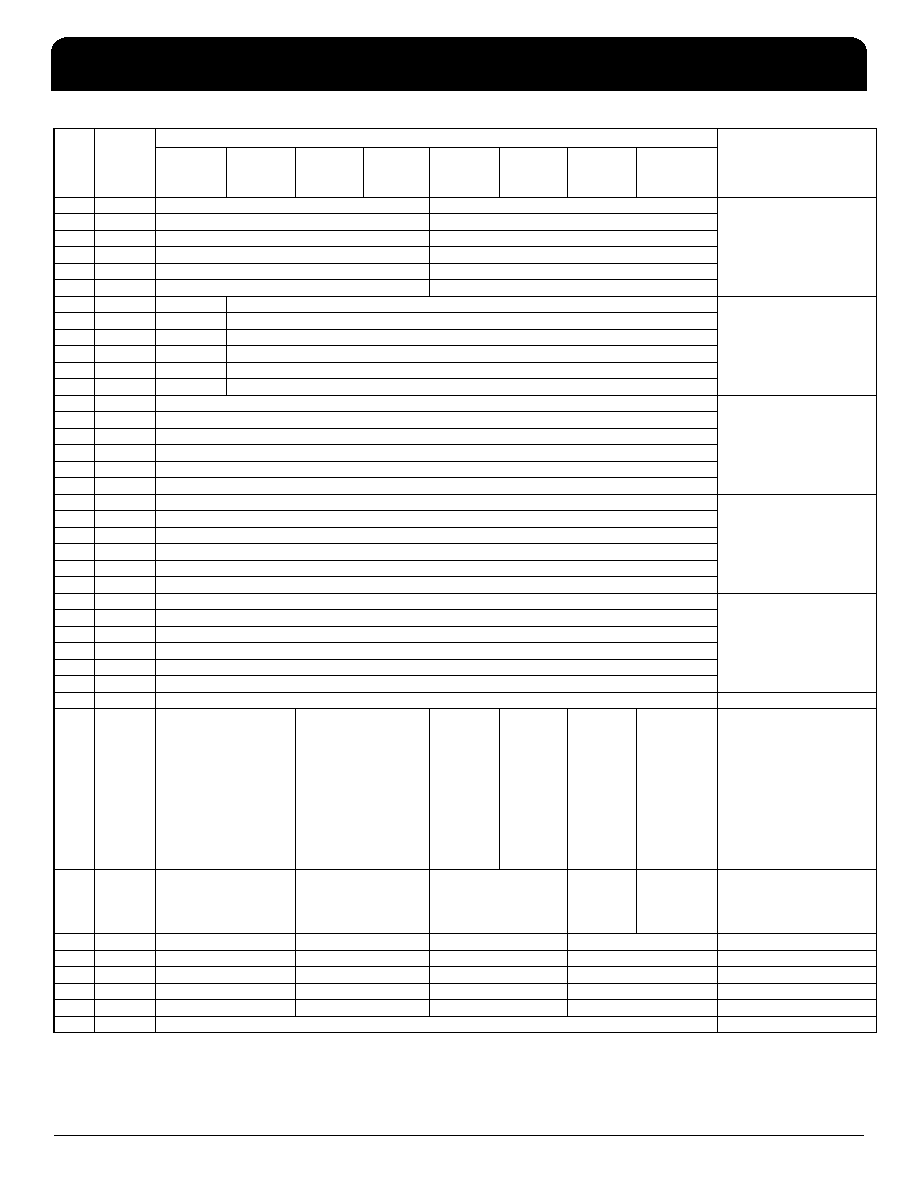

0x56

00

IP3[3:0]_CFG4

RZ3[3:0]_CFG4

PLL3 Loop Parameter

0x57

00

IP3[3:0]_CFG5

RZ3[3:0]_CFG5

0x58

00

IP3[3:0]_CFG0

RZ3[3:0]_CFG0

0x59

00

IP3[3:0]_CFG1

RZ3[3:0]_CFG1

0x5A

00

IP3[3:0]_CFG2

RZ3[3:0]_CFG2

0x5B

00

IP3[3:0]_CFG3

RZ3[3:0]_CFG3

0x5C

03

Reserved

D3[6:0]_CFG0

PLL3 Reference Divide and input

sel

D3[6:0] - 127 step Ref Div

D3 = 0 means power down.

0x5D

03

Reserved

D3[6:0]_CFG1

0x5E

03

Reserved

D3[6:0]_CFG2

0x5F

03

Reserved

D3[6:0]_CFG3

0x60

03

Reserved

D3[6:0]_CFG4

0x61

03

Reserved

D3[6:0]_CFG5

0x62

0C

N3[7:0]_CFG4

N - Feedback Divider

12 - 4095 (values of “0” through

“11” are not allowed)

0x63

0C

N3[7:0]_CFG5

0x64

0C

N3[7:0]_CFG0

0x65

0C

N3[7:0]_CFG1

0x66

0C

N3[7:0]_CFG2

0x67

0C

N3[7:0]_CFG3

0x68

00

SSVCO[7:0]_CFG0

SSVCO[7:0] - PLL3 Spread

Spectrum Loop Feedback

Counter

See Addr 0x80:0x85 for

SSVCO[15:8]

0x69

00

SSVCO[7:0]_CFG1

0x6A

00

SSVCO[7:0]_CFG2

0x6B

00

SSVCO[7:0]_CFG3

0x6C

00

SSVCO[7:0]_CFG4

0x6D

00

SSVCO[7:0]_CFG5

0x6E

00

SS_D3[7:0]_CFG4

SS_D[7:0] - PLL3 Spread

Spectrum Reference Divide

0x6F

00

SS_D3[7:0]_CFG5

0x70

00

SS_D3[7:0]_CFG0

0x71

00

SS_D3[7:0]_CFG1

0x72

00

SS_D3[7:0]_CFG2

0x73

00

SS_D3[7:0]_CFG3

0x74

01

Reserved

0x75

03

OEM0[1:0]

SLEW0[1:0]

INV0

Reserved

S1

S3

Output Controls

S1=1 - OUT1/OUT2 are from

DIV1/DIV2 respectively

S1=0 - Both from DIV2

S3 =1 - OUT3/OUT6 are from

DIV3/DIV6

S3=0 - Both from DIV6

SLEW - see AC Timing

OEM#–output enable mode

x0 - tristated

01 - park low

11 - park high

OEM0 controls OUT0 only

0x76

00

OEM1[1:0]

SLEW1[1:0]

INV1[1:0]

Reserved

Output Controls

INV1 [CLK1, CLK2]

[0] - normal

[1] - invert clock

OEM1 controls OUT1/OUT2

0x77

00

Reserved

SLEW2[1:0]

Reserved

0x78

00

OEM3[1:0]

SLEW3[1:0]

INV3[1:0]

Reserved

OEM3 controls OUT3 and OUT6

0x79

00

OEM4[1:0]

SLEW4[1:0]

INV4[1:0]

Reserved

OEM4 controls OUT4 and OUT4b

0x7A

00

OEM5[1:0]

SLEW5[1:0]

INV5[1:0]

Reserved

OEM5 controls OUT5 and OUT5b

0x7B

00

Reserved

SLEW6[1:0]

Reserved

0x7C

XX1

Reserved

Addr

Default

Register

Hex

Value

Bit #

Description

76

5

4

3

2

1

0

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IDT821024PPG

IC PCM CODEC QUAD NONPROG 44TQFP

IDT821034DNG

IC PCM CODEC QUAD MPI 52-PQFP

IDT821054PQF

IC PCM CODEC QUAD MPI 64-PQFP

IDT82V3001APVG8

IC PLL WAN W/SGL REF INP 56-SSOP

IDT82V3010PVG

IC PLL WAN 51/E1/OC3 DUAL 56SSOP

IDT82V3011PVG

IC PLL WAN T1/E1/OC3 SGL 56-SSOP

IDT82V3012PVG8

IC PLL WAN T1/E1/OC3 DUAL 56SSOP

IDT82V3155PVG

IC PLL WAN T1/E1/OC3 DUAL 56SSOP

相关代理商/技术参数

IDT5V50009DCG

功能描述:IC PC CLOCK 8-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:*

IDT5V50009DCG8

功能描述:IC PC CLOCK 8-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:*

IDT5V50013DCG

功能描述:IC CLK GENERATOR LOW EMI 8-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR)

IDT5V50013DCG8

功能描述:IC CLK GENERATOR LOW EMI 8-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR)

IDT5V50015DCG

功能描述:IC CLK GENERATOR LOW EMI 8SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR)

IDT5V50015DCG8

制造商:Integrated Device Technology Inc 功能描述:IC CLK GENERATOR LOW EMI 8SOIC

IDT5V50015PGG

功能描述:IC CLK GENERATOR LOW EMI 8TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR)

IDT5V50015PGG8

制造商:Integrated Device Technology Inc 功能描述:IC CLK GENERATOR LOW EMI 8TSSOP